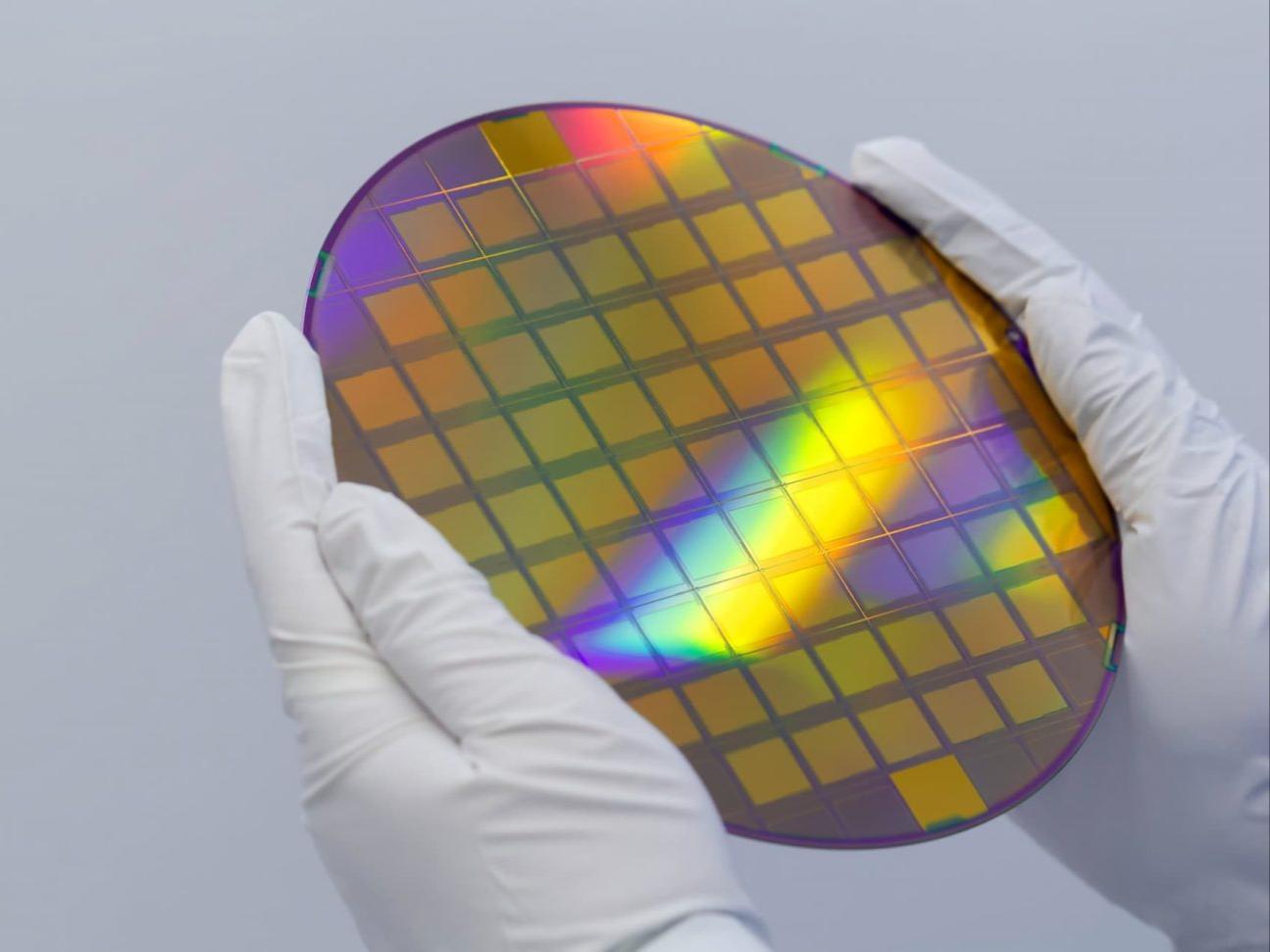

臺(tái)積電(TSMC)近日被曝已在為2026年蘋(píng)果A20系列SoC(系統(tǒng)級(jí)芯片)的封裝,,啟動(dòng)了WMCM(Wafer-Level Multi-Chip Module,晶圓級(jí)多芯片封裝)新工藝試生產(chǎn)準(zhǔn)備工作,。

WMCM是一種在晶圓級(jí)將多顆芯片集成封裝的技術(shù),,能夠在保持高集成度的同時(shí),顯著縮小封裝體積并提升信號(hào)傳輸效率,。

傳統(tǒng)封裝工藝通常在晶圓切割之后,,對(duì)單顆芯片進(jìn)行封裝。先將晶圓鋸切成一顆顆獨(dú)立的芯片,,然后在每顆芯片上進(jìn)行黏附、鍵合或倒裝芯片等工藝,,最后再安裝到塑料或陶瓷封裝基板上,,完成金線或焊球與外部電路板的連接。

傳統(tǒng)封裝工藝流程環(huán)節(jié)多,,芯片在切割和搬運(yùn)過(guò)程中需要多次測(cè)試和運(yùn)輸,,易產(chǎn)生額外的寄生電容和電感,并且封裝后芯片高度不一,,對(duì)散熱和信號(hào)完整性有不利影響,。

WMCM工藝則將多顆芯片在晶圓級(jí)進(jìn)行集成封裝。具體做法是在晶圓上先完成多個(gè)芯片的疊層與重分布層互聯(lián),,然后再整體切割成單個(gè)模塊,。這意味著封裝幾乎在切割前就已完成,大幅減少后續(xù)搬運(yùn)和測(cè)試次數(shù),,降低工藝復(fù)雜度和良率損耗,,并且大幅縮短芯片之間的信號(hào)路徑,降低了寄生電阻,、電容和電感,,從而提升信號(hào)傳輸速率和能效比。

同時(shí),,晶圓級(jí)封裝的平整高度便于散熱管理,,相比傳統(tǒng)封裝中的黏附膠和金線高度差異,,熱阻更低,有助于提升模塊可靠性,。

實(shí)際上,,蘋(píng)果A20芯片作為iPhone 18系列的核心,大概率會(huì)采用TSMC當(dāng)下最先進(jìn)的2納米制程,。盡管2nm制程在晶體管密度和功耗控制上具備優(yōu)勢(shì),,但成本與良率仍是大規(guī)模鋪開(kāi)的障礙。WMCM封裝的引入,,能為蘋(píng)果在不換制程或僅小規(guī)模轉(zhuǎn)移的情況下,,進(jìn)一步提升模組性能和能效比。

原創(chuàng)文章,,作者:houxiangyu,,如若轉(zhuǎn)載,請(qǐng)注明出處:http://hzkljs.com/doc/134322.htm

登錄后才能評(píng)論